This chapter describes the ARM Processor Memory Management Unit.

| 7.1  | Introduction                                           | 7-2  |

|------|--------------------------------------------------------|------|

| 7.2  | MMU Program Accessible Registers                       | 7-3  |

| 7.3  | Address Translation                                    | 7-4  |

| 7.4  | Translation Process                                    | 7-5  |

| 7.5  | Translating Section References                         | 7-8  |

| 7.6  | Translating Small Page References                      | 7-10 |

| 7.7  | Translating Large Page References                      | 7-11 |

| 7.8  | MMU Faults and CPU Aborts                              | 7-12 |

| 7.9  | Fault Address and Fault Status Registers (FAR and FSR) | 7-13 |

| 7.10 | Domain Access Control                                  | 7-14 |

| 7.11 | Fault Checking Sequence                                | 7-15 |

| 7.12 | Interaction of the MMU, IDC and Write Buffer           | 7-18 |

| 7.13 | Effect of Reset                                        | 7-19 |

|      |                                                        |      |

## 7.1 Introduction

The Memory Management MMU performs two primary functions: it translates virtual addresses into physical addresses, and it controls memory access permissions. The MMU hardware required to perform these functions consists of a Translation Lookaside Buffer (TLB), access control logic, and translation table walking logic.

The MMU supports memory accesses based on Sections or Pages. Sections are comprised of 1MB blocks of memory. Two different page sizes are supported: Small Pages consist of 4kB blocks of memory and Large Pages consist of 64kB blocks of memory. (Large Pages are supported to allow mapping of a large region of memory while using only a single entry in the TLB). Additional access control mechanisms are extended within Small Pages to 1kB Sub-Pages and within Large Pages to 16kB Sub-Pages.

The MMU also supports the concept of domains - areas of memory that can be defined to possess individual access rights. The Domain Access Control Register is used to specify access rights for up to 16 separate domains.

The TLB caches 64 translated entries. During most memory accesses, the TLB provides the translation information to the access control logic.

If the TLB contains a translated entry for the virtual address, the access control logic determines whether access is permitted. If access is permitted, the MMU outputs the appropriate physical address corresponding to the virtual address. If access is not permitted, the MMU signals the CPU to abort.

If the TLB misses (it does not contain a translated entry for the virtual address), the translation table walk hardware is invoked to retrieve the translation information from a translation table in physical memory. Once retrieved, the translation information is placed into the TLB, possibly overwriting an existing value. The entry to be overwritten is chosen by cycling sequentially through the TLB locations.

When the MMU is turned off (as happens on reset), the virtual address is output directly onto the physical address bus.

## 7.2 MMU Program Accessible Registers

The ARM Processor provides several 32-bit registers which determine the operation of the MMU. The format for these registers is shown in *•Figure 7-1: MMU register summary* on page 7-3. A brief description of the registers is provided below. Each register will be discussed in more detail within the section that describes its use.

Data is written to and read from the MMU's registers using the ARM CPU's MRC and MCR coprocessor instructions.

The **Translation Table Base Register** holds the physical address of the base of the translation table maintained in main memory. Note that this base must reside on a 16kB boundary.

The **Domain Access Control Register** consists of sixteen 2-bit fields, each of which defines the access permissions for one of the sixteen Domains (D15-D0).

| Register       | 31 | 30                     | 29 | 28 | 27 | 26 | 25 | 24 | 23 22 | 21 2  | 20  | 19 18    | 17  | 7 16     | 15  | 14       | 13 | 12       | 11 | 10 | 9 | 8 | 7 | 6   | 5   | 4  | 3 | 2   | 1   | 0 |

|----------------|----|------------------------|----|----|----|----|----|----|-------|-------|-----|----------|-----|----------|-----|----------|----|----------|----|----|---|---|---|-----|-----|----|---|-----|-----|---|

| <b>1</b> write | 0  | 0                      | 0  | 0  | 0  |    |    |    |       | C     | ont | trol     |     |          |     |          |    |          |    | 0  | R | s | в | 1   | D   | Р  | w | С   | A   | м |

| <b>2</b> write |    | Translation Table Base |    |    |    |    |    |    |       |       |     | •        | •   |          | •   |          | •  | •        |    |    |   |   |   |     |     |    |   |     |     |   |

| <b>3</b> write | 1  | 5                      | 1  | 4  | 1  | 3  | 1  | 2  | 11    | 10    |     | Dom<br>9 | ain | Acc<br>8 | es  | s C<br>7 |    | rol<br>6 | !  | 5  |   | 4 |   | 3   |     | 2  |   | 1   |     | 0 |

| <b>5</b> read  |    |                        |    |    |    |    |    | I  | Fault | Stat  | us  |          |     |          |     |          |    |          | 0  | 0  | 0 | 0 | 1 | Doi | mai | in |   | Sta | atu | S |

| <b>5</b> write |    |                        |    |    |    |    |    |    |       |       |     |          | F   | lusł     | ר T | LB       |    |          |    |    | • |   |   |     |     |    |   |     |     |   |

| <b>6</b> read  |    |                        |    |    |    |    |    |    |       |       |     | F        | Ξaι | ult A    | dd  | res      | S  |          |    |    |   |   |   |     |     |    |   |     |     |   |

| <b>6</b> write |    |                        |    |    |    |    |    | I  | Purge | e Ado | dre | ess      |     |          |     |          |    |          |    |    |   |   |   |     |     |    |   |     |     |   |

|                |    |                        |    |    |    |    |    |    |       |       |     |          |     |          |     |          |    |          |    |    |   |   |   |     |     |    |   |     |     |   |

|                |    |                        |    |    |    |    |    |    |       |       |     |          |     |          |     |          |    |          |    |    |   |   |   |     |     |    |   |     |     |   |

#### Figure 7-1: MMU register summary

Note The registers not shown are reserved and should not be used.

The **Fault Status Register** indicates the domain and type of access being attempted when an abort occurred. Bits 7:4 specify which of the sixteen domains (D15-D0) was being accessed when a fault occurred. Bits 3:1 indicate the type of access being attempted. The encoding of these bits is different for internal and external faults (as indicated by bit 0 in the register) and is shown in **O***Table 7-4: Priority encoding of fault status* on page 7-13. A write to this register flushes the TLB.

The **Fault Address Register** holds the virtual address of the access which was attempted when a fault occurred. A write to this register causes the data written to be treated as an address and, if it is found in the TLB, the entry is marked as invalid. (This operation is known as a TLB purge). The Fault Status Register and Fault Address Register are only updated for data faults, not for prefetch faults.

## 7.3 Address Translation

The MMU translates virtual addresses generated by the CPU into physical addresses to access external memory, and also derives and checks the access permission. Translation information, which consists of both the address translation data and the access permission data, resides in a translation table located in physical memory. The MMU provides the logic needed to traverse this translation table, obtain the translated address, and check the access permission.

There are three routes by which the address translation (and hence permission check) takes place. The route taken depends on whether the address in question has been marked as a section-mapped access or a page-mapped access; and there are two sizes of page-mapped access (large pages and small pages). However, the translation process always starts out in the same way, as described below, with a Level One fetch. A section-mapped access only requires a Level One fetch, but a page-mapped access also requires a Level Two fetch.

## 7.4 Translation Process

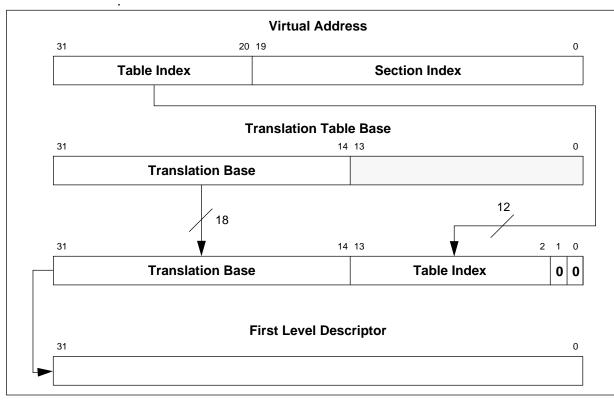

#### 7.4.1 Translation table base

The translation process is initiated when the on-chip TLB does not contain an entry for the requested virtual address. The Translation Table Base (TTB) Register points to the base of a table in physical memory which contains Section and/or Page descriptors. The 14 low-order bits of the TTB Register are set to zero as illustrated in *OFigure 7-2: Translation table base register*; the table must reside on a 16kB boundary.

| 31             | 14 13    | 0 |

|----------------|----------|---|

| Translation Ta | ble Base |   |

#### 7.4.2 Level one fetch

Bits 31:14 of the Translation Table Base register are concatenated with bits 31:20 of the virtual address to produce a 30-bit address as illustrated in **O***Figure 7-3: Accessing the translation table first level descriptors.* This address selects a four-byte translation table entry which is a First Level Descriptor for either a Section or a Page (bit1 of the descriptor returned specifies whether it is for a Section or Page)

Figure 7-3: Accessing the translation table first level descriptors

minar

#### 7.4.3 Level one descriptor

The Level One Descriptor returned is either a Page Table Descriptor or a Section Descriptor, and its format varies accordingly. The following figure illustrates the format of Level One Descriptors.

| 31 | 20                   | 19 1        | 2 11 10 | 9 | 8 5    | 4 | 3 | 2 | 1 | 0 |          |

|----|----------------------|-------------|---------|---|--------|---|---|---|---|---|----------|

|    |                      |             |         |   |        |   |   |   | 0 | 0 | Fault    |

|    | Page Table Ba        | ase Address |         |   | Domain | 1 |   |   | 0 | 1 | Page     |

| ę  | Section Base Address |             | AP      |   | Domain | 1 | С | в | 1 | 0 | Section  |

|    |                      |             |         |   |        |   |   |   | 1 | 1 | Reserved |

|    |                      |             |         |   |        |   |   |   |   |   |          |

#### Figure 7-4: Level one descriptors

The two least significant bits indicate the descriptor type and validity, and are interpreted as shown below.

| Value | Meaning  | Notes                                       |

|-------|----------|---------------------------------------------|

| 0 0   | Invalid  | Generates a Section Translation Fault       |

| 0 1   | Page     | Indicates that this is a Page Descriptor    |

| 10    | Section  | Indicates that this is a Section Descriptor |

| 11    | Reserved | Reserved for future use                     |

Table 7-1: Interpreting level one descriptor bits [1:0]

#### 7.4.4 Page table descriptor

Bits 3:2 are always written as 0.

Bit 4 should be written to 1 for backward compatibility.

**Bits 8:5** specify one of the sixteen possible domains (held in the Domain Access Control Register) that contain the primary access controls.

**Bits 31:10** form the base for referencing the Page Table Entry. (The page table index for the entry is derived from the virtual address as illustrated in *CFigure 7-7: Small page translation* on page 7-10).

If a Page Table Descriptor is returned from the Level One fetch, a Level Two fetch is initiated as described below.

#### 7.4.5 Section descriptor

Bits 3:2 (C, and B) control the cache- and write-buffer-related functions as follows:

C - Cacheable: indicates that data at this address will be placed in the cache (if the cache is enabled).

B - Bufferable: indicates that data at this address will be written through the write buffer (if the write buffer is enabled).

Bit 4 should be written to 1 for backward compatibility.

Bits 8:5 specify one of the sixteen possible domains (held in the Domain Access Control Register) that contain the primary access controls.

Bits 11:10 (AP) specify the access permissions for this section and are interpreted as shown in O Table 7-2: Interpreting access permission (AP) bits on page 7-7. Their interpretation is dependent upon the setting of the S and R bits (control register bits 8 and 9). Note that the Domain Access Control specifies the primary access control; the AP bits only have an effect in client mode. Refer to section on access permissions

| AP | S | R | Permissions<br>Supervisor | User       | Notes                                      |

|----|---|---|---------------------------|------------|--------------------------------------------|

| 00 | 0 | 0 | No Access                 | No Access  | Any access generates a permission fault    |

| 00 | 1 | 0 | Read Only                 | No Access  | Supervisor read only permitted             |

| 00 | 0 | 1 | Read Only                 | Read Only  | Any write generates a permission fault     |

| 00 | 1 | 1 |                           | Re         | served                                     |

| 01 | x | x | Read/Write                | No Access  | Access allowed only in Supervisor mode     |

| 10 | x | x | Read/Write                | Read Only  | Writes in User mode cause permission fault |

| 11 | x | x | Read/Write                | Read/Write | All access types permitted in both modes.  |

| хх | 1 | 1 |                           | Res        | served                                     |

Table 7-2: Interpreting access permission (AP) bits

Bits 19:12 are always written as 0.

Bits 31:20 form the corresponding bits of the physical address for the 1MByte section.

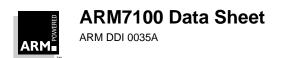

#### **Translating Section References** 7.5

• Figure 7-5: Section translation illustrates the complete Section translation sequence. Note that the access permissions contained in the Level One Descriptor must be checked before the physical address is generated. The sequence for checking access permissions is described below.

Figure 7-5: Section translation

Preliminary

#### 7.5.1 Level two descriptor

If the Level One fetch returns a Page Table Descriptor, this provides the base address of the page table to be used. The page table is then accessed as described in **C***Figure 7-7: Small page translation* on page 7-10, and a Page Table Entry, or Level Two Descriptor, is returned. This in turn may define either a Small Page or a Large Page access. The figure below shows the format of Level Two Descriptors

| 1          | 20 19        | 16 | 15 | 12 | 11 10 | 98  | 7 ( | 65 | 4 3 | 2 | 1 | 0 |            |

|------------|--------------|----|----|----|-------|-----|-----|----|-----|---|---|---|------------|

|            |              |    |    |    |       |     |     |    |     |   | 0 | 0 | Fault      |

| Large Page | Base Address |    |    |    | ap3   | ap2 | apʻ | ap | 0 C | В | 0 | 1 | Large Page |

| Small Page | Base Address |    |    |    | ap3   | ap2 | apʻ | ap | 0 C | В | 1 | 0 | Small Page |

|            |              |    |    |    |       | •   |     | •  |     |   | 1 | 1 | Reserved   |

#### Figure 7-6: Page table entry (Level Two descriptor)

The two least significant bits indicate the page size and validity, and are interpreted as follows.

| Value | Meaning    | Notes                               |

|-------|------------|-------------------------------------|

| 0 0   | Invalid    | Generates a Page Translation Fault  |

| 0 1   | Large Page | Indicates that this is a 64 kB Page |

| 10    | Small Page | Indicates that this is a 4 kB Page  |

| 11    | Reserved   | Reserved for future use             |

Table 7-3: Interpreting page table entry bits 1:0

**Bit 2 B - Bufferable**: indicates that data at this address will be written through the write buffer (if the write buffer is enabled).

Bit 3 C - Cacheable: indicates that data at this address will be placed in the IDC (if the cache is enabled).

**Bits 11:4** specify the access permissions (ap3 - ap0) for the four sub-pages and interpretation of these bits is described earlier in **O***Table 7-1: Interpreting level one descriptor bits [1:0]* on page 7-6.

For large pages, **bits 15:12** are programmed as 0.

**Bits 31:12** (small pages) or bits **31:16** (large pages) are used to form the corresponding bits of the physical address - the physical page number. (The page index is derived from the virtual address as illustrated in *OFigure 7-7: Small page translation* on page 7-10 and *OFigure 7-8: Large page translation* on page 7-11).

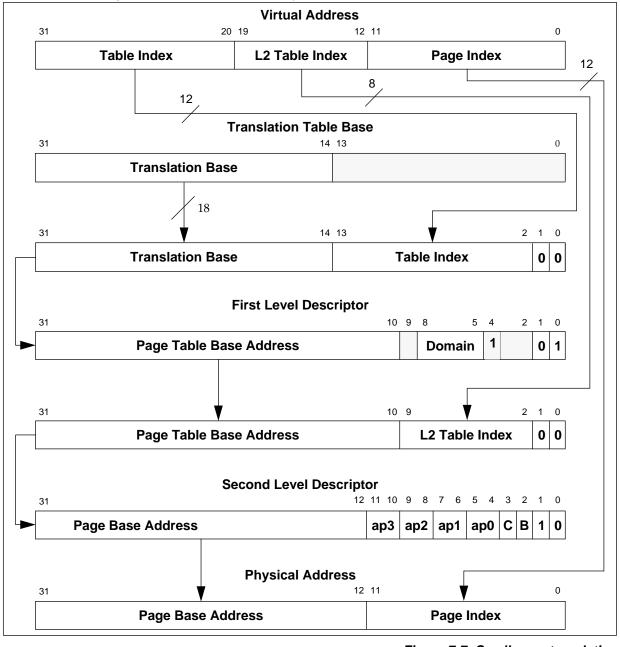

## 7.6 Translating Small Page References

**O***Figure 7-7: Small page translation* illustrates the complete translation sequence for a 4kB Small Page. Page translation involves one additional step beyond that of a section translation: the Level One descriptor is the Page Table descriptor, and this is used to point to the Level Two descriptor, or Page Table Entry. (Note that the access permissions are now contained in the Level Two descriptor and must be checked before the physical address is generated. The sequence for checking access permissions is described later).

ARM7100 Data Sheet ARM DDI 0035A

Preliminary

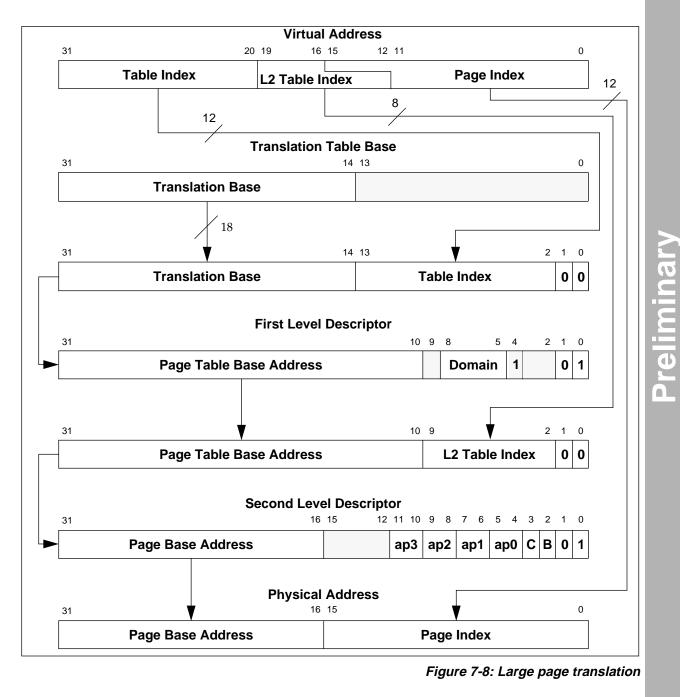

## 7.7 Translating Large Page References

• *Figure 7-8: Large page translation* illustrates the complete translation sequence for a 64 kB Large Page. Note that since the upper four bits of the Page Index and low-order four bits of the Page Table index overlap, each Page Table Entry for a Large Page must be duplicated 16 times (in consecutive memory locations) in the Page Table.

## 7.8 MMU Faults and CPU Aborts

The MMU generates four types of faults:

Alignment Fault

Translation Fault

Domain Fault

Permission Fault

The access control mechanisms of the MMU detect the conditions that produce these faults. If a fault is detected as the result of a memory access, the MMU will abort the access and signal the fault condition to the CPU. The MMU is also capable of retaining status and address information about the abort. The CPU recognises two types of abort: data aborts and prefetch aborts, and these are treated differently by the MMU.

If the MMU detects an access violation, it will do so before the external memory access takes place, and it will therefore inhibit the access.

If the ARM Processor is operating in fastbus mode an internally aborting access may cause the address on the external address bus to change, even though the external bus cycle has been cancelled. The address that is placed on the bus will be the translation of the address that caused the abort, though in the case of the a Translation Fault the value of this address will be undefined. No memory access will be performed to this address.

## 7.9 Fault Address and Fault Status Registers (FAR and FSR)

Aborts resulting from data accesses (data aborts) are acted upon by the CPU immediately, and the MMU places an encoded 4-bit value FS[3:0], along with the 4-bit encoded Domain number, in the Fault Status Register (FSR). In addition, the virtual processor address which caused the data abort is latched into the Fault Address Register (FAR). If an access violation simultaneously generates more than one source of abort, they are encoded in the priority given in **C***Table 7-4: Priority encoding of fault status* on page 7-13.

CPU instructions on the other hand are prefetched, so a prefetch abort simply flags the instruction as it enters the instruction pipeline. Only when (and if) the instruction is executed does it cause an abort; an abort is not acted upon if the instruction is not used (ie. it is branched around). Because instruction prefetch aborts may or may not be acted upon, the MMU status information is not preserved for the resulting CPU abort; for a prefetch abort, the MMU does not update the FSR or FAR.

The sections that follow describe the various access permissions and controls supported by the MMU and detail how these are interpreted to generate faults.

|         | Source                  |                  | FS[3210]     | Domain[3:0]     | FAR            |

|---------|-------------------------|------------------|--------------|-----------------|----------------|

| Highest | Alignment               |                  | 00x1         | х               | valid          |

|         | Bus Error (translation) | level1<br>level2 | 1100<br>1110 | x<br>valid      | valid<br>valid |

|         | Translation             | Section<br>Page  | 0101<br>0111 | Note 2<br>valid | valid<br>valid |

|         | Domain                  | Section<br>Page  | 1001<br>1011 | valid<br>valid  | valid<br>valid |

|         | Permission              | Section<br>Page  | 1101<br>1111 | valid<br>valid  | valid<br>valid |

|         | Bus Error (linefetch)   | Section<br>Page  | 0100<br>0110 | valid<br>valid  | valid<br>valid |

| Lowest  | Bus Error (other)       | Section<br>Page  | 1000<br>1010 | valid<br>valid  | valid<br>valid |

Table 7-4: Priority encoding of fault status

x is undefined, and may read as 0 or 1

#### Notes

- 1 Any abort masked by the priority encoding may be regenerated by fixing the primary abort and restarting the instruction.

- 2 In fact this register will contain bits[8:5] of the Level 1 entry which are undefined, but would encode the domain in a valid entry.

ARM7100 Data Sheet

## 7.10 Domain Access Control

MMU accesses are primarily controlled via domains. There are 16 domains, and each has a 2-bit field to define it. Two basic kinds of users are supported: Clients and Managers. Clients use a domain; Managers control the behaviour of the domain. The domains are defined in the Domain Access Control Register. *•Figure 7-9: Domain access control register format* on page 7-14 illustrates how the 32 bits of the register are allocated to define the sixteen 2-bit domains.

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 | 3 2 1 | 54 | 1 6 | 98 | 11 10 | 13 12 | 15 14 | 17 16 | 19 18 | 21 20 | 23 22 | 25 24 | 27 26 | 29 28 | 1 30 | 3 |

|-------------------------------------------------------------------------------------|-------|----|-----|----|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|---|

|-------------------------------------------------------------------------------------|-------|----|-----|----|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|---|

Figure 7-9: Domain access control register format

• *Table 7-5: Interpreting access bits in domain access control register* defines how the bits within each domain are interpreted to specify the access permissions.

| Value | Meaning   | Notes                                                                                                  |

|-------|-----------|--------------------------------------------------------------------------------------------------------|

| 00    | No Access | Any access will generate a Domain Fault.                                                               |

| 01    | Client    | Accesses are checked against the access permission bits in the Section or Page descriptor.             |

| 10    | Reserved  | Reserved. Currently behaves like the no access mode.                                                   |

| 11    | Manager   | Accesses are NOT checked against the access Permission bits so a Permission fault cannot be generated. |

Table 7-5: Interpreting access bits in domain access control register

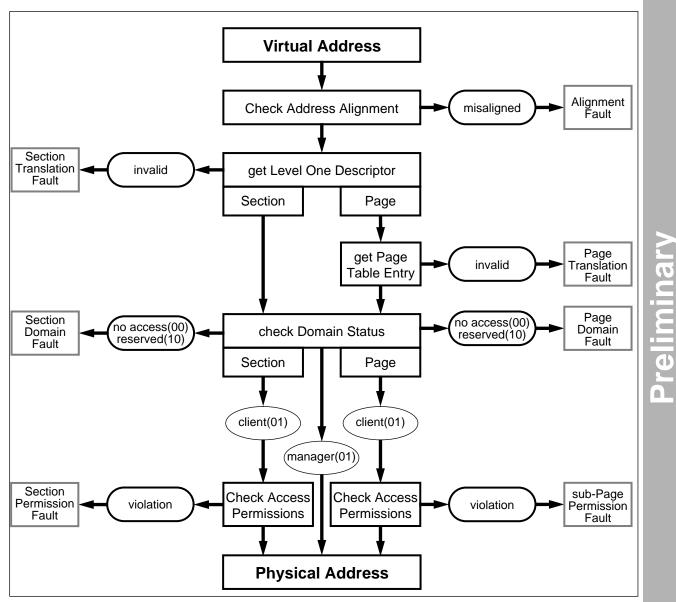

## 7.11 Fault Checking Sequence

The sequence by which the MMU checks for access faults is slightly different for Sections and Pages. The figure below illustrates the sequence for both types of accesses. The sections and figures that follow describe the conditions that generate each of the faults.

Figure 7-10: Sequence for checking faults

#### 7.11.1 Alignment fault

If Alignment Fault is enabled (bit 1 in Control Register set), the MMU will generate an alignment fault on any data word access the address of which is not word-aligned irrespective of whether the MMU is enabled or not; in other words, if either of virtual address bits [1:0] are not 0. Alignment fault will not be generated on any instruction fetch, nor on any byte access. Note that if the access generates an alignment fault, the access sequence will abort without reference to further permission checks.

#### 7.11.2 Translation fault

There are two types of translation fault: section and page.

- 1 A Section Translation Fault is generated if the Level One descriptor is marked as invalid. This happens if bits[1:0] of the descriptor are both 0 or both 1.

- 2 A Page Translation Fault is generated if the Page Table Entry is marked as invalid. This happens if bits[1:0] of the entry are both 0 or both 1.

#### 7.11.3 Domain fault

There are two types of domain fault: section and page. In both cases the Level One descriptor holds the 4-bit Domain field which selects one of the sixteen 2-bit domains in the Domain Access Control Register. The two bits of the specified domain are then checked for access permissions as detailed in **C***Table 7-2: Interpreting access permission (AP) bits* on page 7-7. In the case of a section, the domain is checked once the Level One descriptor is returned, and in the case of a page, the domain is checked once the Page Table Entry is returned.

If the specified access is either No Access (00) or Reserved (10) then either a Section Domain Fault or Page Domain Fault occurs.

#### 7.11.4 Permission fault

There are two types of permission fault: section and sub-page. Permission fault is checked at the same time as Domain fault. If the 2-bit domain field returns client (01), then the permission access check is invoked as follows:

#### section:

If the Level One descriptor defines a section-mapped access, then the AP bits of the descriptor define whether or not the access is allowed according to **C***Table 7-2: Interpreting access permission (AP) bits* on page 7-7. Their interpretation is dependent upon the setting of the S bit (Control Register bit 8). If the access is not allowed, then a Section Permission fault is generated.

#### sub-page:

If the Level One descriptor defines a page-mapped access, then the Level Two descriptor specifies four access permission fields (ap3..ap0) each corresponding to one quarter of the page. Hence for small pages, ap3 is selected by the top 1kB of the page, and ap0 is selected by the bottom 1kB of the page; for large pages, ap3 is selected by the top 16kB of the page, and ap0 is selected by the bottom 16kB of the page. The selected AP bits are then interpreted in exactly the same way as for a section (see **C***Table 7-2: Interpreting access permission (AP) bits* on page 7-7), the only difference being that the fault generated is a sub-page permission fault.

### 7.12 Interaction of the MMU, IDC and Write Buffer

The MMU, IDC and WB may be enabled/disabled independently. However, in order for the write buffer or the cache to be enabled the MMU must also be enabled. There are no hardware interlocks on these restrictions, so invalid combinations will cause undefined results.

| MMU | IDC | WB  |

|-----|-----|-----|

| off | off | off |

| on  | off | off |

| on  | on  | off |

| on  | off | on  |

| on  | on  | on  |

Table 7-6: Valid MMU, IDC and write buffer combinations

The following procedures must be observed.

#### To enable the MMU:

- 1 Program the Translation Table Base and Domain Access Control Registers

- 2 Program Level 1 and Level 2 page tables as required

- 3 Enable the MMU by setting bit 0 in the Control Register.

**Note** Care must be taken if the translated address differs from the untranslated address as the two instructions following the enabling of the MMU will have been fetched using "flat translation" and enabling the MMU may be considered as a branch with delayed execution. A similar situation occurs when the MMU is disabled. Consider the following code sequence:

MOV R1, #0x1 MCR 15,0,R1,0,0 ; Enable MMU Fetch Flat Fetch Flat Fetch Translated

#### To disable the MMU:

- 1 Disable the WB by clearing bit 3 in the Control Register.

- 2 Disable the IDC by clearing bit 2 in the Control Register.

- 3 Disable the MMU by clearing bit 0 in the Control Register.

- **Note** If the MMU is enabled, then disabled and subsequently re-enabled the contents of the TLB will have been preserved. If these are now invalid, the TLB should be flushed before re-enabling the MMU.

Disabling of all three functions may be done simultaneously.

## 7.13 Effect of Reset

See O4.7 Reset on page 4-16.

This chapter details the programmable registers for ARM7100.

| 8.1 | Introduction          | 8-2 |

|-----|-----------------------|-----|

| 8.2 | Summary of Registers  | 8-3 |

| 8.3 | Register Descriptions | 8-5 |

## 8.1 Introduction

ARM7100 contains internal programmable registers in addition to those in the ARM processor.

The registers internal to ARM7100 are all programmed by writing to memory locations 8000.0000 to 8000.FFFF. Accessing memory in this range will not cause any external bus activity unless broadcast mode is enabled. Any access to the undefined range from 8000.1000 to C000.0000 will have no effect.

Writes to bits that are not explicitly defined in the internal area are legal and will have no effect. Reads from bits not explicitly defined in the internal area are legal but will read undefined values.

It is only possible to access internal addresses as 32-bit words and they are always on a word boundary, except for the PIO port registers which can be accessed as bytes. Each internal register is valid for 256 bytes, since address bits in the range A[0:5] are not decoded, for example, the SYSFLG register appears at locations 8000.0140 to 8000.017C. The PIO port registers are byte wide but can be accessed as a word. These registers additionally decode A0 and A1.

## 8.2 Summary of Registers

### Key

✓ X

| can write/read |

|----------------|

|                |

do not write/read

| Name    | Address   | Size | Read | Write | Function                                           |

|---------|-----------|------|------|-------|----------------------------------------------------|

| PADR    | 8000.0000 | 8    | 1    | 1     | Port A data register.                              |

| PBDR    | 8000.0001 | 8    | 1    | 1     | Port B data register.                              |

| PCDR    | 8000.0002 | 8    | 1    | 1     | Port C data register.                              |

| PDDR    | 8000.0003 | 8    | 1    | 1     | Port D data register.                              |

| PADDR   | 8000.0040 | 8    | 1    | 1     | Port A data direction register.                    |

| PBDDR   | 8000.0041 | 8    | 1    | 1     | Port B data direction register.                    |

| PCDDR   | 8000.0042 | 8    | 1    | 1     | Port C data direction register.                    |

| PDDDR   | 8000.0043 | 8    | 1    | 1     | Port D data direction register.                    |

| PEDR    | 8000.0080 | 4    | 1    | 1     | Port E data register.                              |

| PEDDR   | 8000.00C0 | 4    | 1    | 1     | Port E data direction register.                    |

| SYSCON  | 8000.0100 | 32   | 1    | 1     | System control register                            |

| SYSFLG  | 8000.0140 | 32   | 1    | x     | System status flags.                               |

| MEMCFG1 | 8000.0180 | 32   | 1    | 1     | Expansion and ROM memory configuration register 1. |

| MEMCFG2 | 8000.01C0 | 32   | 1    | 1     | Expansion and ROM memory configuration register 2. |

| DRFPR   | 8000.0200 | 8    | 1    | 1     | DRAM refresh period register.                      |

| INTSR   | 8000.0240 | 16   | 1    | x     | Interrupt status register.                         |

| INTMR   | 8000.0280 | 16   | 1    | 1     | Interrupt mask register.                           |

| LCDCON  | 8000.02C0 | 32   | 1    | 1     | LCD control register.                              |

| TC1D    | 8000.0300 | 16   | 1    | 1     | Read-write data to TC1.                            |

| TC2D    | 8000.0340 | 16   | 1    | 1     | Read-write data to TC2.                            |

| RTCDR   | 8000.0380 | 32   | 1    | 1     | Real time clock data register.                     |

| RTCMR   | 8000.03C0 | 32   | 1    | 1     | Real time clock match register.                    |

| PMPCON  | 8000.0400 | 12   | 1    | 1     | DC to DC pump control register.                    |

Table 8-1: ARM7100 registers

Preliminary

| Name     | Address                  | Size | Read | Write | Function                                              |

|----------|--------------------------|------|------|-------|-------------------------------------------------------|

| CODR     | 8000.0440                | 8    | 1    | 1     | CODEC data I/O register.                              |

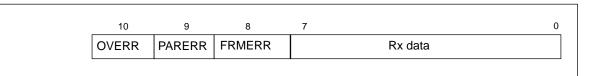

| UARTDR   | 8000.0480                | 8    | 1    | 1     | UART FIFO data register.                              |

| UBLCR    | 8000.04C0                | 32   | 1    | 1     | UART bit rate and line control register.              |

| SYNCIO   | 8000.0500                | 16   | 1    | 1     | Synchronous serial I/O data register                  |

| PALLSW   | 8000.0540                | 32   | 1    | 1     | Least significant 32-bit word of LCD palette register |

| PALMSW   | 8000.0580                | 32   | 1    | 1     | Most significant 32-bit word of LCD palette register  |

| STFCLR   | 8000.05C0                | -    | x    | 1     | Write to clear all start up reason flags.             |

| BLEOI    | 8000.0600                | -    | x    | 1     | Write to clear battery low interrupt.                 |

| MCEOI    | 8000.0640                | -    | x    | 1     | Write to clear <b>MEDCHG</b> interrupt.               |

| TEOI     | 8000.0680                | -    | x    | 1     | Write to clear tick and watchdog interrupt.           |

| TC1EOI   | 8000.06C0                | -    | x    | 1     | Write to clear TC1 interrupt.                         |

| TC2EOI   | 8000.0700                | -    | x    | 1     | Write to clear TC2 interrupt.                         |

| RTCEOI   | 8000.0740                | -    | x    | 1     | Write to clear RTC match interrupt.                   |

| UMSEOI   | 8000.0780                | -    | X    | 1     | Write to clear UART modem status changed interrupt.   |

| COEOI    | 8000.07C0                | -    | x    | 1     | Write to clear CODEC sound interrupt                  |

| HALT     | 8000.0800                | -    | x    | 1     | Write to enter idle state                             |

| STDBY    | 8000.0840                | -    | x    | 1     | Write to enter standby state                          |

| Reserved | 8000.0880 -<br>8000.0FFF | -    |      |       | Write will have no effect, read is undefined          |

Table 8-1: ARM7100 registers (Continued)

## 8.3 Register Descriptions

All internal registers in ARM7100 are reset (cleared to zero) by a system reset (**nPOR**, **nRESET** or **nPWRFL** signals becoming active), except for the DRAM refresh period register (DRFPR) which is only reset by **nPOR** becoming active. This ensures that the contents of DRAM are preserved though a user reset or power fail condition. Additionally, the real time clock registers are only cleared by **nPOR**.

#### 8.3.1 Port A data register (PADR)

Values written to this 8-bit read-write register are output on port A pins if the corresponding data direction bits are set HIGH (port output). Values read from this register reflect the external state of port A, not necessarily the value written to it. All bits are cleared by a system reset.

### 8.3.2 Port B data register (PBDR)

Values written to this 8-bit read-write register are output on port B pins if the corresponding data direction bits are set HIGH (port output). Values read from this register reflect the external state of port B, not necessarily the value written to it. All bits are cleared by a system reset.

### 8.3.3 Port C data register (PCDR)

Values written to this 8-bit read-write register are output on port C pins if the corresponding data direction bits are set LOW (port output). Values read from this register reflect the external state of port C, not necessarily the value written to it. All bits are cleared by a system reset.

#### 8.3.4 Port D data register (PDDR)

Values written to this 8-bit read-write register are output on port D pins if the corresponding data direction bits are set LOW (port output). Values read from this register reflect the external state of port C, not necessarily the value written to it. All bits are cleared by a system reset.

### 8.3.5 Port A data direction register (PADDR)

Bits set in this 8-bit read-write register select the corresponding pin in port A to become an output. Clearing a bit sets the pin to input. All bits are cleared by a system reset.

#### 8.3.6 Port B data direction register (PBDDR)

Bits set in this 8-bit read-write register select the corresponding pin in port B to become an output. Clearing a bit sets the pin to input. All bits are cleared by a system reset.

#### 8.3.7 Port C data direction register (PCDDR)

Bits cleared in this 8-bit read-write register select the corresponding pin in port C to become an output. Setting a bit sets the pin to input. All bits are cleared by a system reset so that port C is output by default.

#### 8.3.8 Port D data direction register (PDDDR)

Bits cleared in this 8-bit read-write register select the corresponding pin in port D to become an output, setting a bit sets the pin to input. All bits are cleared by a system reset so that port D is output by default.

#### 8.3.9 Port E data register (PEDR)

Values written to this 4-bit read-write register will be output on port E pins if the corresponding data direction bits are set HIGH (port output). Values read from this register reflect the external state of port E, not necessarily the value written to it. All bits are cleared by a system reset.

#### 8.3.10 Port E data direction register (PDDDR)

Bits set in this 4-bit read-write register will select the corresponding pin in port E to become an output, clearing bit sets the pin to input. All bits are cleared by a system reset so that port E is input by default.

### 8.3.11 The system control register (SYSCON)

The system control register is a 21-bit read /write register controlling all the general configuration of ARM7100 as well as operating modes for peripheral devices. All bits in this register are cleared by a system reset.

The bits in the system control register SYSCON are shown in *Figure 8-1: The system* control register.

| 7     | 6      | 5      | 4     | 3       |        |          | 0      |

|-------|--------|--------|-------|---------|--------|----------|--------|

| TC2S  | TC2M   | TCIS   | ТСІМ  |         | Keyboa | ard scan |        |

|       | 1      |        |       |         |        |          |        |

| 15    | 14     | 13     | 12    | 11      | 10     | 9        | 8      |

| SIREN | CDENRX | CDENTX | LCDEN | DBGEN   | BZMOD  | BZTOG    | UARTEN |

|       |        |        |       |         |        |          |        |

| 23    | 22     | 21     | 20    | 19      | 18     | 17       | 16     |

|       |        |        | IRTXM | WAKEDIS | EXCKEN | ADCł     | KSEL   |

#### Figure 8-1: The system control register

Keyboard scan

This 4-bit field defines the state of the keyboard column drives. OTable 8-2: Keyboard scan field gives definitions of these states.

|         | Keyboard Scan                                                      | Column                                                                                                                                                                          |  |  |  |  |

|---------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|         | 0                                                                  | All driven HIGH                                                                                                                                                                 |  |  |  |  |

|         | 1                                                                  | All driven LOW                                                                                                                                                                  |  |  |  |  |

|         | 2 - 7                                                              | All Tristate                                                                                                                                                                    |  |  |  |  |

|         | 8                                                                  | Column 0 only driven HIGH                                                                                                                                                       |  |  |  |  |

|         | 9                                                                  | Column 1 only driven HIGH                                                                                                                                                       |  |  |  |  |

|         | 10                                                                 | Column 2 only driven HIGH                                                                                                                                                       |  |  |  |  |

|         | 11                                                                 | Column 3 only driven HIGH                                                                                                                                                       |  |  |  |  |

|         | 12                                                                 | Column 4 only driven HIGH                                                                                                                                                       |  |  |  |  |

|         | 13                                                                 | Column 5 only driven HIGH                                                                                                                                                       |  |  |  |  |

|         | 14                                                                 | Column 6 only driven HIGH                                                                                                                                                       |  |  |  |  |

|         | 15                                                                 | Column 7 only driven HIGH                                                                                                                                                       |  |  |  |  |

|         |                                                                    | Table 8-2: Keyboard scan field                                                                                                                                                  |  |  |  |  |

| TC1M    |                                                                    | Timer counter 1 mode. Setting this bit sets TC1 to prescale mode. Clearing it sets free running mode.                                                                           |  |  |  |  |

| TC1S    |                                                                    | Timer counter 1 clock source. Setting this bit sets the TC1 clock source to 512 KHz. Clearing it sets the clock source to 2KHz.                                                 |  |  |  |  |

| TC2M    |                                                                    | Timer counter 2 mode. Setting this bit sets TC2 to prescale mode. Clearing it sets free running mode.                                                                           |  |  |  |  |

| TC2S    |                                                                    | Timer counter 2 clock source. Setting this bit sets the TC2 clock source to 512 KHz. Clearing it sets the clock source to                                                       |  |  |  |  |

| UARTEN  | Internal UART ena<br>UART.                                         | ble bit. Setting this bit enables the internal                                                                                                                                  |  |  |  |  |

| BZTOG   | This bit is used to a                                              | drive the <b>BUZ</b> output directly.                                                                                                                                           |  |  |  |  |

| BZMOD   | This bit sets the BI                                               | UZ output mode:                                                                                                                                                                 |  |  |  |  |

|         |                                                                    | nnected directly to the BZTOG bit                                                                                                                                               |  |  |  |  |

| ADCKSEL | Microwire / SPI per<br>selects the frequer<br>the frequency of the | ripheral clock speed select. This 2-bit field<br>hcy of the ADC sample clock. This is twice<br>e synchronous serial ADC interface clock.<br>CLK frequencies shows the available |  |  |  |  |

|            | ADCKSEL                                                                             | ADC Sample<br>Frequency (kHz)                                                                                                                                                                                                                                    | ADC Interface<br>Frequency (kHz)                                                                                                                          |

|------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 00                                                                                  | 8                                                                                                                                                                                                                                                                | 4                                                                                                                                                         |

|            | 01                                                                                  | 32                                                                                                                                                                                                                                                               | 16                                                                                                                                                        |

|            | 10                                                                                  | 128                                                                                                                                                                                                                                                              | 64                                                                                                                                                        |

|            | 11                                                                                  | 256                                                                                                                                                                                                                                                              | 128                                                                                                                                                       |

| DBGEN      | all internal a<br>to expansion<br>active in its<br>interrupt req<br>processor a     | bit enables debug/broadca<br>ccesses are output as if the<br>n memory addressed by C<br>standard address range. I<br>juest and the fast interrupt<br>re output on port E bits 1 a<br>/ internal strobe                                                           | ey were reads or writes<br>CS6. CS6 will still be<br>In addition the internal<br>t request signals to the                                                 |

| LCDEN      | Setting this                                                                        | bit enables the LCD contr                                                                                                                                                                                                                                        | oller.                                                                                                                                                    |

| CDENTX     |                                                                                     | erface enable Tx bit. Settir<br>erface for data transmissic<br>vice.                                                                                                                                                                                             | 0                                                                                                                                                         |

| CDENRX     |                                                                                     | erface enable Rx bit. Settin<br>rface for data reception fro                                                                                                                                                                                                     |                                                                                                                                                           |

| SIREN      | SIR protoco<br>UART is not                                                          | l encoding enable bit. This<br>enabled.                                                                                                                                                                                                                          | s has no effect if the                                                                                                                                    |

| EXCLKEN    | is enabled c<br>the CPU clo<br>is running. T<br>consumption<br>the <b>EXPCLH</b> wi | bansion clock enable. If this<br>continuously with the same<br>ck and will free run all the f<br>his bit should not be left so<br>n reasons. If the system en<br>$\mathbf{X}$ will become undefined.<br>If be active during memory<br>we external wait state gen | e speed and phase as<br>time the main oscillator<br>et all the time for power<br>nters the standby state<br>If this bit is clear<br>y cycles to expansion |

| WAKEDIS    | Switch on vi                                                                        | a the wakeup input is disa                                                                                                                                                                                                                                       | abled if this bit is set.                                                                                                                                 |

| IRTXM      | strategy. Cle<br>represented<br>Setting this I<br>of width 3/16<br>1.6µSec reg      | de bit. This bit controls the<br>earing it means each zero<br>as a pulse of width 3/16th<br>bit means each zero bit is<br>6th of the period of 115,00<br>ardless of the selected bit<br>wer but probably reduce to                                               | bit transmitted is<br>h of the bit rate period.<br>represented as a pulse<br>00 bit rate clock ie.<br>rate. Setting this bit will                         |

| BITS 21-31 | Reserved. V                                                                         | Vrite will have no effect, w                                                                                                                                                                                                                                     | ill always read zero.                                                                                                                                     |

ARM7100 Data Sheet

### 8.3.12 The System Status Flags Register (SYSFLG)

The system status flags register (SYSFLG) is a 32-bit read only register which indicates various system information. The bits in SYSFLG are defined in **O***Figure 8-2: The System Status Flag Register* and are described below.

| 7      |       |          | 4        | 3        | 2       | 1     | 0     |

|--------|-------|----------|----------|----------|---------|-------|-------|

|        | DID   |          |          | WUON     | WUDR    | DCDET | MCDR  |

| 15     | 14    | 13       | 12       | 11       | 10      | 9     | 8     |

| CLDFLG | PFFLG | RSTFLG   | NBFLG    | UBUSY    | DCD     | DSR   | CTS   |

| 23     | 22    | 21       |          |          |         |       | 16    |

| UTXFF  | UTXFE |          |          | RTCDIV   |         |       |       |

| 31     | 30    | 29       | 28       | 27       | 26      | 25    | 24    |

| VE     | ERID  | Reserved | Reserved | BOOT8BIT | SSIBUSY | CTXFF | CRXFE |

|        |       |          |          |          |         |       |       |

#### Figure 8-2: The System Status Flag Register

| MCDR  | This bit reflects the non-latched status of the media changed input.                                                                                                                                                                                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCDET | This bit reflects the inverted state of the <b>nEXTPWR</b> input pin.                                                                                                                                                                                                                                                            |

| WUDR  | Wake up direct read. This bit reflects the non-latched state of the <b>WAKEUP</b> signal.                                                                                                                                                                                                                                        |

| WUON  | This bit is set if the system has been brought out of standby<br>by a rising edge on the <b>WAKEUP</b> signal. It is only cleared by<br>a system reset or by writing to the HALT or STDBY locations.                                                                                                                             |

| DID   | Display ID nibble. This 4-bit nibble reflects the latched state<br>of the 4 LCD data lines <b>DO[3:0</b> ]. The state of the 4 LCD data<br>lines is latched by the LCDEN bit and so always reflects the<br>last state of these lines before the LCD controller was<br>enabled. These bits identify the LCD display panel fitted. |

| CTS   | This bit reflects the current status of the clear to send (CTS) modem control input to the built in UART.                                                                                                                                                                                                                        |

| DSR   | This bit reflects the current status of the data set ready (DSR) modem control input to the built in UART.                                                                                                                                                                                                                       |

| DCD   | This bit reflects the current status of the data carrier detect (DCD) modem control input to the built in UART.                                                                                                                                                                                                                  |

| UBUSY    | UART transmitter busy. Set while the internal UART is busy transmitting data, it is guaranteed to remain set until the complete byte has been sent, including all stop bits.                                                                                                                                                             |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NBFLG    | The new battery flag bit is set if a LOW to HIGH transition has occurred on the <b>nBATCHG</b> input. It is cleared by writing to the STFCLR location.                                                                                                                                                                                   |

| RSTFLG   | The reset flag is set if the <b>nURESET</b> input has been forced LOW. It is cleared by writing to the STFCLR location.                                                                                                                                                                                                                  |

| PFFLG    | The Power Fail Flag is set if the system has been reset by the <b>PWRFL</b> input pin. It is cleared by writing to the STFCLR location.                                                                                                                                                                                                  |

| CLDFLG   | The cold start flag is set if ARM7100 has been reset with a power on reset. It is cleared by writing to the STFCLR location.                                                                                                                                                                                                             |

| RTCDIV   | This 6-bit field reflects the number of 64Hz ticks that have passed since the last increment of the RTC. It is the output of the divide by 64 chain that divides the 64Hz tick clock down to 1Hz for the RTC. The MSB is the 32Hz output, the LSB is the 1Hz output.                                                                     |

| URXFE    | UART receiver FIFO empty. The meaning of this bit depends<br>on the state of the UFIFOEN bit in the UART bit rate and line<br>control register. If the FIFO is disabled, this bit is set when the<br>Rx holding register is empty. If the FIFO is enabled the<br>URXFE bit will be set when the Rx FIFO is empty.                        |

| UTXFF    | UART transmit FIFO full. The meaning of this bit depends on<br>the state of the UFIFOEN bit in the UART bit rate and line<br>control register. If the FIFO is disabled, this bit is set when the<br>Tx holding register is full. If the FIFO is enabled the UTXFF<br>bit will be set when the Tx FIFO is full.                           |

| CRXFE    | The CODEC Rx FIFO empty bit is set if the 16 byte CODEC Rx FIFO is empty.                                                                                                                                                                                                                                                                |

| CTXFF    | The CODEC Tx FIFO full bit is set if the 16 byte CODEC Tx FIFO is full.                                                                                                                                                                                                                                                                  |

| SSIBUSY  | The synchronous serial interface busy bit is set while data is being shifted in or out of the synchronous serial interface. When clear, data is valid to read.                                                                                                                                                                           |

| Reserved | This will always read zero.                                                                                                                                                                                                                                                                                                              |

| VERID    | Version ID bits. These 2 bits determine the revision id for ARM7100. It will read 0 for the first revision.                                                                                                                                                                                                                              |

| BOOT8BIT | This bit indicates the default (power on reset) bus width of the ROM interface. If set, the initial bus width will be 8 bits. If clear, it will be 32 bits. See <b>O</b> <i>8.3.13 Memory configuration register 1 (MEMCFG1)</i> on page 8-11 and <b>O</b> <i>8.3.14 Memory configuration register 2 (MEMCFG2)</i> on page 8-11 for more |

details on the ROM interface bus width. The state of this bit is determined by the state of Port E bit 0 during power on reset. LOW during power on reset will clear the BOOT8BIT bit and the system will boot from a 32-bit ROM. HIGH during power on reset will set the BOOT8BIT bit and the system will boot from an 8-bit ROM.

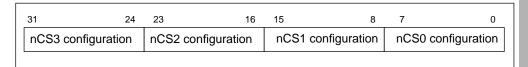

### 8.3.13 Memory configuration register 1 (MEMCFG1)

The memory configuration register 1 is a 32-bit read-write register which sets the configuration of the four expansion and ROM selects **nCS[0:3]**. Each select is configured with a one byte field, starting with expansion select 0.

### 8.3.14 Memory configuration register 2 (MEMCFG2)

The memory configuration register 2 is a 32-bit read-write register which sets the configuration of the four expansion and ROM selects **CS[4:7**]. Each select is configured with a one byte field, starting with expansion select 4.

| 31          | 24 | 23       | 16 | 15 | 8            | 7     | 0            |

|-------------|----|----------|----|----|--------------|-------|--------------|

| CS7 configu |    | CS6 cont |    |    | onfiguration | CS4 c | onfiguration |

|             |    |          |    |    |              |       |              |

#### Figure 8-4: Memory configuration register 2

Each of the 8-bit fields in the memory configuration registers are identical and define the number of wait states, define the bus width, enable the **EXPCLK** output during accesses and enable sequential mode access. This is shown in *CFigure 8-5: Byte fields in the memory configuration register* below.

|   | 7     | 6     | 5          | 4                 | 3            | 2            | 1     | 0     |

|---|-------|-------|------------|-------------------|--------------|--------------|-------|-------|

| ( | CLKEN | SQAEN | Sequential | Access Wait State | Random Acces | s Wait State | Bus V | Vidth |

Figure 8-5: Byte fields in the memory configuration register

**○***Table 8-4: Values of the bus width field* defines the bus width field. The effect of this field is dependent on the BOOT8BIT bit which can be read in the SYSFLG register. All bits in the memory configuration register are cleared by a system reset and the state of the BOOT8BIT bit is determined by Port E bit 0 pin on ARM7100 during power on reset. In this way, pulling Port E bit 0 either LOW or HIGH during power on reset allows ARM7100 to boot from either 32-bit wide or 8-bit wide ROMs.

| Bus Width Field | BOOT8BIT | Expansion Transfer Mode | Port E bit 0 during power on reset |  |  |

|-----------------|----------|-------------------------|------------------------------------|--|--|

| 00              | 0        | 32-bit wide bus access  | LOW                                |  |  |

| 01              | 0        | 16-bit wide bus access  | LOW                                |  |  |

| 10              | 0        | 8-bit wide bus access   | LOW                                |  |  |

| 11              | 0        | PCMCIA mode             | LOW                                |  |  |

| 00              | 1        | 8-bit wide bus access   | HIGH                               |  |  |

| 01              | 1        | PCMCIA mode             | HIGH                               |  |  |

| 10              | 1        | 32-bit wide bus access  | HIGH                               |  |  |

| 11              | 1        | 16-bit wide bus access  | HIGH                               |  |  |

Table 8-4: Values of the bus width field

When the bus width field is programmed to PCMCIA mode the bus width and bus conversion is defined by the state of A[27] and A[26]. ©*Table 8-5: PCMCIA mode bus widths* on page 8-12 defines the bus width and bus conversion for values of A[27] and A[26]. Word bus conversion converts an ARM 32-bit word access into a series of byte or 16-bit accesses. A special case is 16-bit I/O accesses (A[26] and A[27] HIGH). In this case, 32-bit ARM word accesses are not converted into two 16-bit accesses. This is to allow individual 16-bit register access. In this mode D[16:31] will be invalid and the output expansion address bit 1 is selected by the value of A[25]. ARM7100 will always output 0 on expansion address bit 25, ie. in 16-bit I/O mode processor address bit 25 becomes PCMIA address bit 1, and PCMIA address bit 25 is 0 limiting the 16-bit I/O address space to 32 Mb.

**Note** 16-bit I/O accesses are not converted to 32-bit ARM word accesses. This means that D[16:31] will be invalid during ARM word accesses to this memory area.

| A26 | A27 | Bus Width | Word Bus Conversion | PCMCIA Memory Area            |  |  |

|-----|-----|-----------|---------------------|-------------------------------|--|--|

| 0   | 0   | 8 Bits    | Yes                 | 8-bit attribute memory access |  |  |

| 1   | 0   | 16 Bits   | Yes                 | 16-bit common memory access   |  |  |

| 0   | 1   | 8 Bits    | Yes                 | 8-bit I/O access              |  |  |

| 1   | 1   | 16 Bits   | No                  | 16-bit I/O access             |  |  |

Table 8-5: PCMCIA mode bus widths

• *Table 8-7: Values of the page mode access wait state field* defines the values of the Random access wait state field.

| Value | No. Wait States | Required Random Access Speed (nSEC) |

|-------|-----------------|-------------------------------------|

| 00    | 4               | 250                                 |

| 01    | 3               | 200                                 |

| 10    | 2               | 150                                 |

| 11    | 1               | 100                                 |

Table 8-6: Values of the random access wait state field

• *Table 8-7: Values of the page mode access wait state field* defines the values of the page mode access wait state field.

| Value | No. Wait States | Required Random Access Speed (nSEC) |

|-------|-----------------|-------------------------------------|

| 00    | 3               | 150                                 |

| 01    | 2               | 120                                 |

| 10    | 1               | 80                                  |

| 11    | 0               | 40                                  |

Table 8-7: Values of the page mode access wait state field

| SQAEN | Sequential access enable. Setting this bit enables sequential accesses that are on a quad word boundary to take advantage of faster access times from devices that support page mode. The sequential access will be faulted after four words, (to allow video refresh cycles to occur) even if the access is part of a longer sequential access. |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKEN | Expansion clock enable. Setting this bit enables the <b>EXPCLK</b> to be active during accesses to the selected expansion device. This provides a timing reference for devices that need to extend bus cycles using the <b>EXPRDY</b> input. Back to back (but not necessarily page mode) accesses result in a continuous clock.                 |

For more details on bus timing, refer to OChapter 20, DC and AC Parameters.

#### 8.3.15 DRAM refresh period register (DRFPR)

The DRAM refresh period register is an 8-bit read-write register which enables refresh and selects the refresh period used by the DRAM controller for its periodic CAS before RAS refresh. The value in the DRAM refresh period register is only cleared by a *power on reset*. Its state is maintained during a power fail or user reset.

ARM7100 Data Sheet

| 7      | 6 | 0                                                                                                                                                                                                                        |

|--------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RFSHEN |   | RFDIV                                                                                                                                                                                                                    |

|        |   |                                                                                                                                                                                                                          |

| RFSHEN |   | DRAM refresh enable. Setting this bit enables periodic refresh cycles to be generated by ARM7100 at a rate set by the RFDIV field. Setting this bit also enables self refresh mode when ARM7100 is in the standby state. |

| RFDIV  |   | This 7-bit field sets the DRAM refresh rate. The refresh period is derived from a 128 KHz clock and is given by the following formula:                                                                                   |

|        |   | Frequency (KHz) = 128/(RFDIV + 1)                                                                                                                                                                                        |

|        |   | or                                                                                                                                                                                                                       |

|        |   | RFDIV = (128/Refresh frequency (KHz)) - 1                                                                                                                                                                                |

The maximum refresh frequency is 64 KHz, the minimum is 1KHz. The RFDIV field should not be programmed with zero as this results in no refresh cycles being initiated.

### 8.3.16 Interrupt status register (INTSR)

The interrupt status register is a 16-bit read only register. It reflects the current state of the 16 interrupt sources within ARM7100. Each bit is set if the appropriate interrupt is active. The interrupt assignment is given in **•***Figure 8-6: Interrupt Assignment*.

| 7      | 6      | 5      | 4      | 3     | 2     | 1     | 8      |

|--------|--------|--------|--------|-------|-------|-------|--------|

| EINT3  | EINT2  | EINT1  | CSINT  | MCINT | WEINT | BLINT | EXTFIQ |

|        |        |        |        |       |       |       |        |

| 15     | 14     | 13     | 12     | 11    | 10    | 9     | 8      |

| SSEOTI | UMSINT | URXINT | UTXINT | TINT  | RTCMI | TC2OI | TC10I  |

|        | •      |        |        |       |       |       |        |

#### Figure 8-6: Interrupt Assignment

EXTFIQ The external fast interrupt is active if the nEXTFIQ input pin is forced LOW and is mapped to the nFIQ input on the ARM7 processor.

BLINT Battery low interrupt is active if no external supply is present (nEXTPWR is HIGH) and the battery OK input pin BATOK is forced LOW. This interrupt is de-glitched with a 16 KHz clock so only generates an interrupt if it is active for longer than 62.5 mSec. It is mapped to the nFIQ input on the ARM7 processor and is cleared by writing to the BLEOI location.

| WEINT | Watch dog expired interrupt becomes active on a rising edge<br>of the periodic 64 Hz tick interrupt clock if the tick interrupt is<br>still active, ie. if a tick interrupt has not been serviced for a<br>complete tick period. It is cleared by writing to the TEOI<br>location.                                                                |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCINT | This interrupt is active after a rising edge on the <b>MEDCHG</b><br>input pin has been detected, This input is de-glitched with a<br>16 KHz clock so only generates an interrupt if it is active for<br>longer than 62.5 mSec. It is mapped to the <b>FIQ</b> input on the<br>ARM7 processor and is cleared by writing to the MCEOI<br>location. |

| CSINT | The CODEC sound interrupt is active if the CODEC interface<br>is enabled and the CODEC data FIFO has reached half full or<br>empty (depending on the interface direction). It is cleared by<br>writing to the COEOI location.                                                                                                                     |

| EINT1 | The external interrupt input 1 is active if the <b>nEINT1</b> input is active (LOW). It is cleared by returning <b>nEINT1</b> to the passive (HIGH) state.                                                                                                                                                                                        |

| EINT2 | The external interrupt input 2 is active if the <b>NEINT2</b> input is active (LOW). It is cleared by returning <b>nEINT2</b> to the passive (HIGH) state.                                                                                                                                                                                        |

| EINT3 | External interrupt input 3. This input will be active if the <b>EINT3</b> input is active (HIGH). It is cleared by returning <b>EINT3</b> to the passive (LOW) state.                                                                                                                                                                             |

| TC10I | The TC1 under flow interrupt becomes active on the next rising edge of the timer counter 1 clock after the timer counter has under flowed (reached zero). It is cleared by writing to the TC1EOI location.                                                                                                                                        |